# **ELECTRONICS & COMMUNICATION ENGINEERING**

## Dr. K. Vasanth

Associate Professor & Head Teaching Experience: 17 Years Contact No.: +91-9790760740 Email: hod\_ece@cbit.ac.in

GENESIS: The Department was established in the year 1979 along with the inception of the institution. It offers Two UG programs one in ECE and the other in Electronics Engineering (VLSI Design & Technology). It also offers two PG programs one in Communication Engineering and the other in Embedded Systems & VLSI Design. The department has been continuously Striving for excellence in engineering education and research, attracting meritorious students to seek admission. The Department has good infrastructural facilities. In addition, an exclusive Navigation and Communication Research Centre(NCRC) is established with support from SAC ISRO and G-One Lab. Department also has VLSI Lab supported bu CDAC under Meity C2S project. The Students are provided with greater exposure in core areas of Electronics & Communication Engineering. The students are encouraged to participate in the technigcal & research activities other than the undergoing regular curriculam.

#### VISION

To emerge as a vibrant model of excellence in education, research and innovation in Electronics and Communication Engineering.

#### MISSION

- To import strong theoretical and practical knowledge of the state of art technologies to meet growing challege in the industry.

- To carry out the advanced and need based research in consultation with the renowned research and industrial organizations.

- To create entrepreneurship environment including innovation, incubation and encourage patent the work.

# TEACHING STAFF STAFF O7 Professors O1 Adjunct Professor O9 Associate Professors Assistant Professors

- 80% of the faculty have Ph.D from Reputed Organizations around the globe.

- ✓ Faculties have expertise in various areas such as Signal Processing, Communications & Networking, Digital Systems, Embedded Systems and IoT, VLSI and RF & Microwave Engineering.

- Faculty has guided **52** Doctorates and **35** are recently pursuing under our faculty

8 NON-TEACHING STAFF Well qualified and experienced

## PROFESSIONAL SOCIETIES/CLUBS

✓ IEEE CBIT Student Branch, IEEE Signal Processing Society, Student Branch Chapter, IETE Student Forum IEEE Circuits and Systems Society, Student Branch Chapter, IEEE WIE affinity group, Makers of India Robotics and Innovation Club, HAM Radio Club.

# PROGRAMS OFFERED

B.E [Electronics and Communication Engineering] Accredited for 6 times by NBA, Intake-180

B.E [Electronics Engineering (VLSI Design & Technology) Intake-60

M.E [Communication Engineering] Accredited for 3times by NBA Intake-12

M.E [Embedded Systems and VLSI Design] Accredited by NBA Intake-12

# COMPANIES VISITED FOR PLACEMENT/PROMINENT MOUS

#### PROMINENT MOUS

- → Bits Pilani, M/s Bitsilica Pvt. Ltd.

- → ACD Communications Pvt. Ltd.

- → College Bag Pvt. Ltd.

- → Regional Telecom Training Centre, BSNL

- → National Instruments, Bangalore

- → Advanced Micro Devices Inc, JNTU Kakinada

- → Space Applications Centre (SAC), ISRO, Ahmedabad

- → Constelli Signals Pvt. Ltd., Hyderabad

- Megasynth Technologies Pvt. Ltd.

- → Pi Square Technologies Pvt. Ltd.

- → Regional Telecom Training Centre, BSNL

- Quinfosystems Pvt. Ltd.

- Indian Society for VLSI Education (ISVE) Ranchi, Jharkhand, India

# SPONSORED PROJECTS/CONSULTANCY

- → Department has successfully executed 8 Sponsored Projects and 6 Consultancy Projects to the tune of above ₹1.75 crores sponsoring agencies such as AICTE, ISRO, DRDO, DST, MeitY etc.,

- Projects with ₹350.55 Lacs from government & non-government agencies are currently carried out.

#### STUDENTS ACHIEVEMENTS

- Sreshta Vejju and team of ECE Students clinched first position at the recent Technical Project Expo competition 'Inventex' held at Osmania University. Their project was recognized for its innovative approach to long-range Satellite Communication technology.

- Student of ECE Rahul Tej Mora (Team Name: omega outliers) received first Prize of 25000/- in Mathedemia 24 on 17/05/2024.

- ✓ Bhavyasri and team received Triumph in "Fempreneur -2024" which was organized by Cowe, Telangana held on 27th March 2024 and achieved 2nd position for pitching their idea of "Compact paddy dryers".

- Shruthi Laya and team Dhaanyagunah received the championship of LevUp ideathon, a challenging 3 level competition. Their groundbreaking idea earned them the top spot and a 1 lakh prize pool.

- ✓ Our students stood runner up in robo sumo at BITS HYDERABAD, Name: N Thishan Reddy, Roll no. 160123735120, Branch: ECE-2 3rd semester, Competetion venue: BITS pilani hyderabad campus, Event name: ATMoS 2024Competion name: robosumo, Prize: 2nd place (runners up), Event lasted from 8th - 10th November 2024.

- K. Giridhar Reddy, of 3rd year ECE has won best paper award in the SCEECS 2025 IEEE conference held at NIT, Bhopal on 18th and 19th January 2025.

- Best Paper and poster award National Tech Symposium at ECE dept, University college of Engineering, Osmania University by K Giridhar Reddy of 3rd year ECE on 21st march 2025

- Best Paper Award at VANSH 2025, Paper presentation competition at Vignan Institute of Technology and Science by K Giridhar Reddy, 160122735040 of 3rd year ECE on 20th march 2025.

- 2nd Prize at NAFED08 conference by ISRO, VSSC at IIT Hyderabad by K. Giridhar Reddy, 160122735040 and V.Bhavya Sri, 161022735301 of 3rd year ECE on February 1st 2025.

- Nptel STAR Felicitation event at IIT Madras by K Giridhar Reddy of 3rd year ECE on February 9th, 2025.

#### INFRASTRUCTURE HIGHLIGHTS

The Department has excellent infrastructure of 11 class rooms and 14 laboratories with high-end equipment and the latest software with LAN connections, 1 big seminar hall, one E-class room, and a department library apart from the central library, and waiting rooms for girl students. Inadditions, an exclusive Navigation and Communication Research Centre(NCRC) is established. The department provides access to high end softwares: MatLab, LabView, Cadence Tools, Mentor Graphics, Xilinx, Windriver's Vx- Works, Multisim, IE3D, Work View Office and NS Tools etc. Tow (IRNSS-SPS-GPS and IRNSS-GPS-SBAS) receivers sponsored by SAC-ISRO under MoU are installed for field trials and data collection and three IRNSS-GPS-SBAS receivers sponsored by SAC-ISRO under NaVIC-GAGAN utilization program are also available along with RF Field Fox analyzer to conduct research.

Patents: Granted: 11, Published: 29

B.E III Year Devineni Manogna offered internship by Google IT-Services India Private Ltd for AY 2023-24 and offered the stipend of ₹1.25L per month.

#### **INTERNSHIPS**

Students are doing internships in the following reputed Companies/organizations. BHEL, BEL, HCU, Defense Labs, RCI, AAI, ECIL, BDL, NI, BSNL, and various companies- Synapsys, Silicon Labs, MOSCHIP, Oracle and LTI Mind Tree, Constellia Signals.

University Internship at Hyderabad (HCU) is scheduled for 4 weeks from June 16th June 2025 to 11th July 2025.

STAR PNT TIRUPATI offered Internships for AY 2025-26

BE IV Year Vivek Pothamshetty offered internship by F5 Networks for AY 2024-25 and offered the stipend of Rs.75,000 per month.

BEIV Year P.T. Sai Sri Charan offered internship by AMS semiconductor India Pvt. Ltd. for AY 2025-26 and offered the stipend of Rs.30,000 per month.

#### **CBIT IN NEWS**

The Ministry of Electronics and Information Technology has sanctioned a project under Chip to Startup Programme Category-II, to Chaitanya Bharathi Institute of Technology (CBIT) in collaboration with Osmania University. The duration of the project is 5-years. Starting from September 2023.

The main aim of the C2S project is to build indigenous IP cores for National semiconductor IP repository. The Secondary aim of the project is to train & develop highly skilled Manpower for the upcoming semiconductor eco-system under Indian Semiconductor Mission.

The Project aims to design and develop silicon proven high resolution All Digital Phase Locked Loop (ADPLL) IP Core.

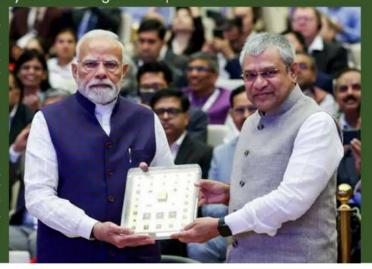

The first tape-out of the proposed IP was designed at CBIT and was fabricated at SCL Chandigarh. It was an honourable moment for CBIT when the our indigenous IC, as part of collage was presented to honourable PM Modi by the minister of Electronics and IT on the occasion of SemiCOn INDIA 2025 Inagural.

# **CBIT Joins India's Semiconductor Mission**

DECCAN NEWS SERVICE HYDERABAD

Chaitanya Bharathi Institute of Technology (CBIT) has marked a proud milestone by contributing to India's first indigenous semiconductor initiative under the Ministry of Electronics and Information Technology's (MeitY) Chips to Startup (C2S) program. The institute's expertise in VLSI design and advanced chip development has placed it at the forefront of the nation's semiconductor mission.

A chip designed and fabri-cated by CBIT was featured in a "collage of chips" presented to Prime Minister Narendra Modi by Union Minister Ashwini Vaishnaw during Semi-con India 2025 in New Delhi on September 2. This recognition highlights CBIT's role in advancing the Atmanirbhar Bharat vision of self-reliance in semiconductor design and manufacturing.

achievement The through the successful design of an All-Digital Phase-Locked Loop (ADPLL) chip, developed in collaboration Osmania University under the C2S program.

CBIT President N. Subash commended the research team for their dedication and assured continued support for advancing research and innovation. Principal Prof. C.V. Narasimhulu congratulated the faculty and students involved, calling it a proud moment that places CBIT on par with premier institutions like the IITs in research and industry collaboration.

The project was led by: Dr. Mohd. Ziauddin Jahangir (Chief Investigator) Dr. D. Krishna Reddy (Co-

Chief Investigator)

Mrs. P. Shirisha and Ms. P. Charishma (Project Staff) A group of dedicated PG and UG students of CBIT.

CBIT has recently introduced a dedicated VLSI course into its undergraduate curriculum, ensuring students gain industry-relevant skills and exposure to cutting-edge

technology. This initiative, supported by Dr. A.D. Sarma, Advisor of R&D, and Dr. K. Vasanth, Head of ECE, reflects the institute's long-term commitment to contributing to India's emerging semiconduc-tor ecosystem. With this tor ecosystem. With this breakthrough, CBIT has reinforced its reputation as a leading research and innovation hub in Telangana, contributing significantly to the nation's strategic goal of semiconductor self-reliance.

# CENTER OF EXCELLENCE/ INDUSTRY INITIATED RESEARCH LABS

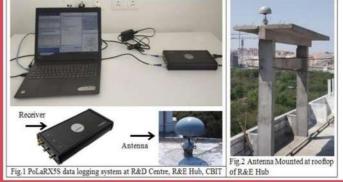

Navigation and Communication Research Centre (NCRC) was established in the year 2014 with support from SAC, ISRO Ahmedabad, with a vision to develop a full-fledged Centre of Excellence (CoE) for carrying out advanced Research and impart Training in the areas of Navigation NCRC Communication. equipped with state-of-art equipment in the field of Navigation and Communication. One such equipment is PolaRx5S GNSS Scintillation Monitoring Receiver worth of 16 Lakhs sponsored by Department of Science and Technology Govt. of India. Other major Fig. 1 PoLaRXSS data logging system at R&D Centre, R&E Hub, CBIT of R&E Hub

equipment includes IRNSS SPS GPS receiver and IRNSS GPS SBAS receiver (Accord Software & Systems Pvt. Ltd.), worth 6 lakhs each, provided by SAC, ISRO Ahmedabad. NCRC has made remarkable contributions and the major outcomes include:

- >> Research projects worth nearly ₹1.5 Crore, sanctioned by prestigious funding agencies such as DST, DRDO, ISRO, and AICTE.

- >> More than 40 publications in reputed Journals and leading Conferences

- >> Training programs in collaboration with reputed research organizations such as DRDO labs, AICTE and renowned Academic Institutions such as IIT Guwahati, NIT Warangal and Osmania University

- >> MoUs with academic institutions and Industry such as SAC, ISRO Ahmedabad, JNTUK and ACD Communication, Hyderabad.

# MEITY SPONSORED VLSI LAB UNDER C2S SCHEME

The Lab was established on 16th September 2023 under Chip to silicon scheme of Meity. The Lab consists of Industry utilized softwares such as Cadence EDA, Synopsys EDA, Siemens EDA, Ansys EDA, Vivado. The Lab also has State of Art Development boards such as Pynq Z2, Boolean Board, Urban Board, Arty A7-100T, Kria KR-260, Kria KV (video), Pynq ZU, Zynq Ultrascale+ MPSoC ZCUI. The Lab had been sanctioned by Ministry of electronics and information technology (MeitY) worth Rs 1.91 crores under Chip to startup (C2S) - Category-II Phase-I for "The Design Fabrication and Development of Silicon Proven IP core for High Resolution ADPLL". The lab offers Internship, Projects to the students and trained more than 300 Students in the field of VLSI Design through periodic awareness.

#### ALUMNI ACHIEVEMENTS

Ms. Akhila, Alumni of 2023 batch is selected in Telangana Police Department.

Jeevan Reddy, Alumni of 2019 batch is appreciated by Honorable Chief Minister & IT Minister of TS Government for his achievements as a young entrepreneur.

R.V. Hara Prasad, Outstanding Scientist DLRL, DRDO, Hyderabad.

# **NOTABLE ALUMNI**

Sri Komma Siva Prakash Reddy, Senior Member Technical Staff, Oracle India Pvt. Ltd. Bangalore.

Sri Satish Pattapu, IRS, Assistant Commissioner, Indian Customs, Mumbai.

Allipuram Rajasekhar Reddy, Managing Director Brio Factors Technologies India Pvt. Ltd. Hyderabad, Entrepreneur.